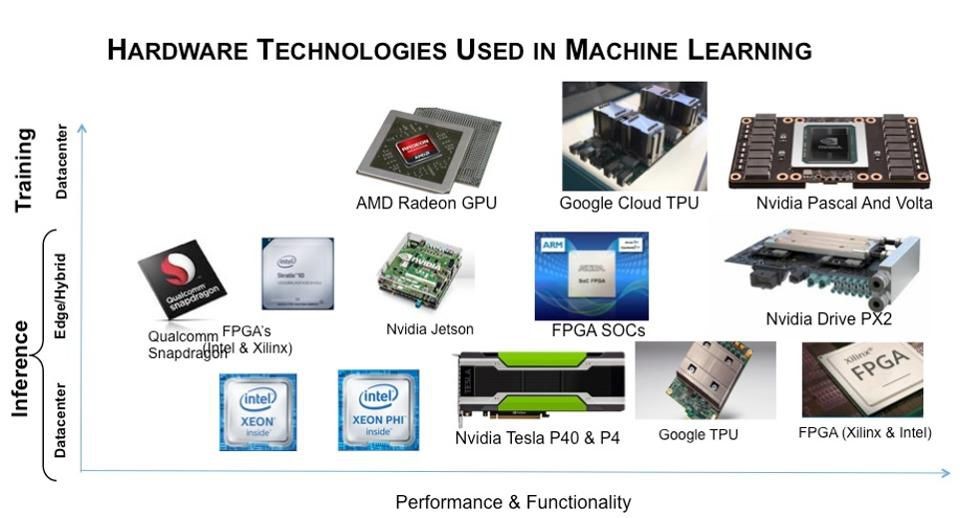

Future Internet | Free Full-Text | An Updated Survey of Efficient Hardware Architectures for Accelerating Deep Convolutional Neural Networks

GitHub - coleblackman/TIDENet: TIDENet is an ASIC written in Verilog for Tiny Image Detection at Edge with neural networks (TIDENet) using DNNWeaver 2.0, the Google SkyWater PDK, OpenLANE, and Caravel.

Intel Nervana Neural Network Processors (NNP), premiers ASICs conçus pour l'IA et le Deep Learning – DCmag

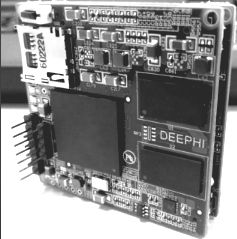

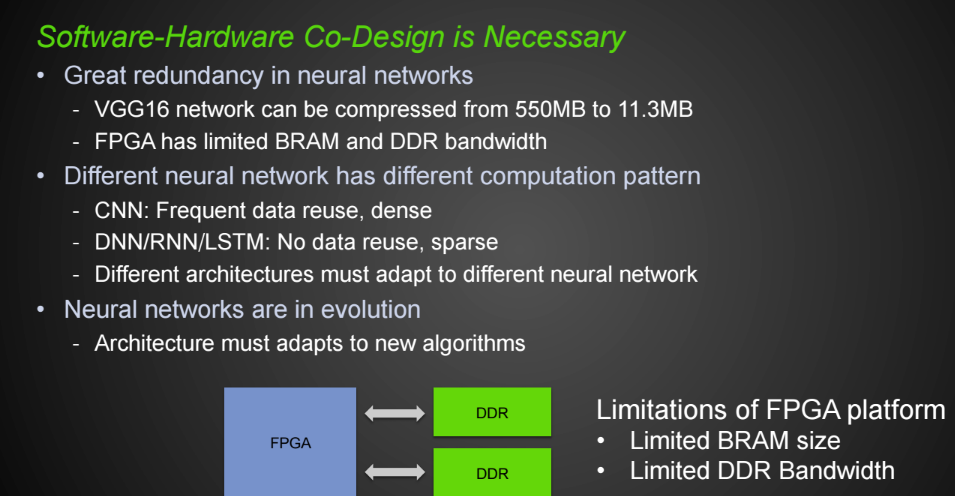

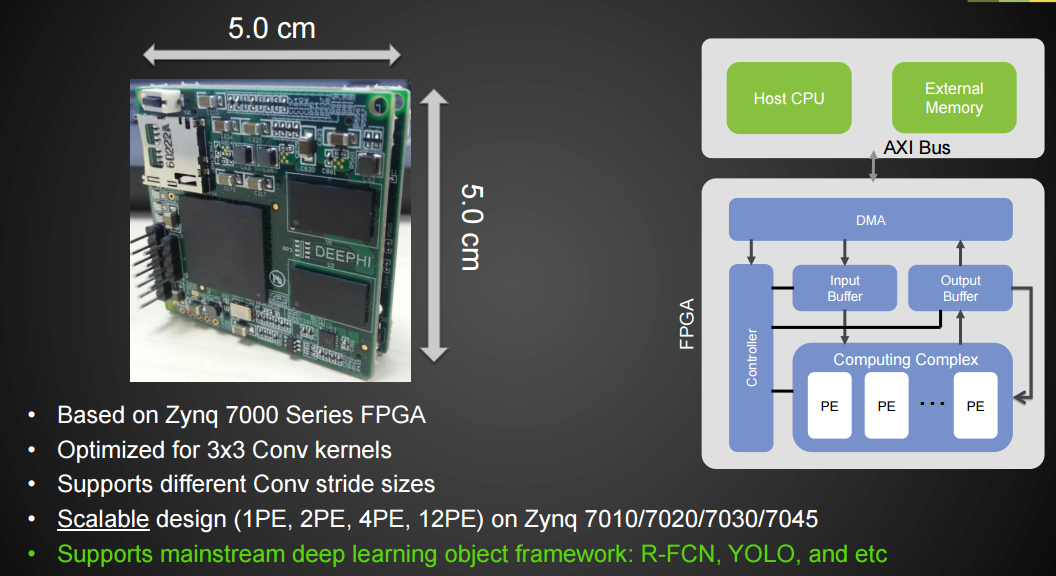

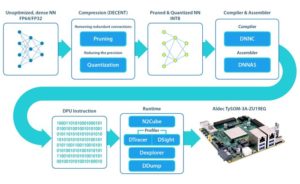

Blog: Aldec Blog - How to develop high-performance deep neural network object detection/recognition applications for FPGA-based edge devices - FirstEDA