Sanders -RASSP Project - Parwan - CPU Dataflow VHDL Codes by Zainalabedin Navabi, 1996. Designed by Funda Kutay, and last updated 11/05/1996

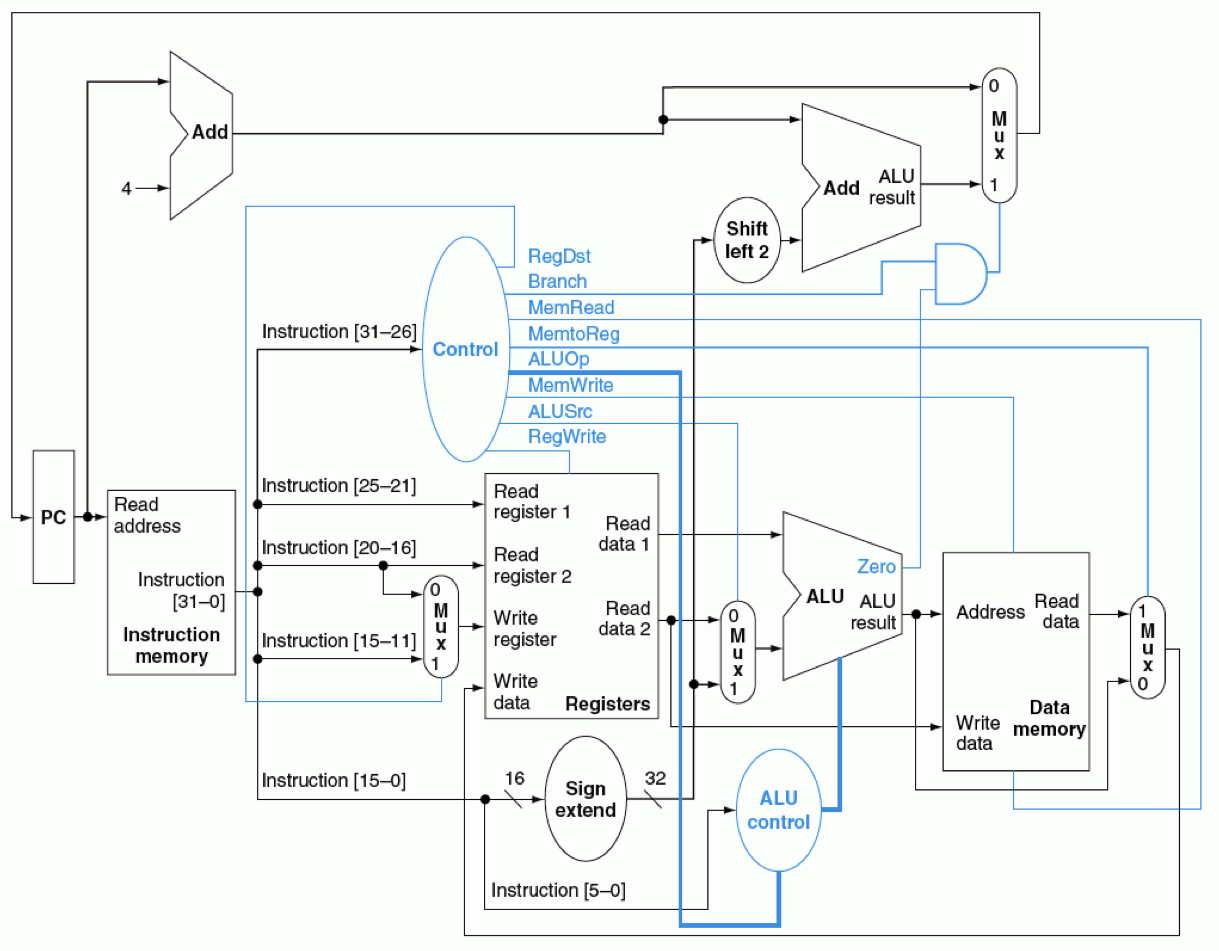

GitHub - bveyseloglu/Single-and-Multi-Cycle-MIPS-CPU-Design: A very simple single cycle and multi cycle MIPS CPU design written in VHDL. The design explained in detail.